Report by Soy-de TV – Interview with Carlos Pardo: Soy-de TV talked to our CEO about the semiconductor factory he wants to set up in Tres Cantos. Read more

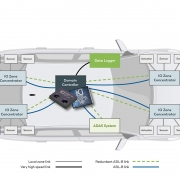

This video about automotive multi-gigabit optical connectivity presents the standardized solution under development by KDPOF to reach a 50 Gb/s bit rate over 40 meters of wiring harness. In the process, we’ll comply with the hardest OEM’s EMC specs, and meeting all automotive requirements in terms of operational temperature, reliability, ageing, mechanical loads, chemical loads, dirtiness and harsh environments in general. And all this with outstanding low power and low cost. Please, follow us to the KDPOF labs and we’ll show you a demo of our multi-gigabit solution: 50 Gb/s optical transmission for automotive.

KDPOF will give insight on “Automotive Communications Standards” at the IEEE Conference “Use of Standards in Industry: IoT, Robotics, Automotive, and Communications” on 20 April 2022 in Madrid, Spain. The IEEE event will discuss the importance of the different standards and their use and impact on the industry in different sectors such as automotive, communications, satellites, etc. In his presentation, Luis Manuel Torres, Principal Engineer at KDPOF and Editor-in-Chief of the IEEE 802.3cz standardization project “Multi-gigabit Optical Automotive Ethernet”, will give a general view of the most important automotive standards, with special emphasis on in-vehicle communication standards.

Tasks and Responsibilities

- Implement ASIC / SoCs / FPGAs for multiple products, starting at the specification & design phase, continuing through technology selection, implementation, and validation. Innovation in performance, power and cost to build the best possible product is a must.

- Participate in all phases of ASIC / FPGA design flow (Synthesis, Place & Route, and Timing Closure) as required.

- Work with backend teams to address any layout and timing issues for ASICs.

- Verification by emulation with FPGAs in the lab.

- Involvement in lead-up, validation, characterization and qualification phases of ASICs.

KDPOF

KDPOF